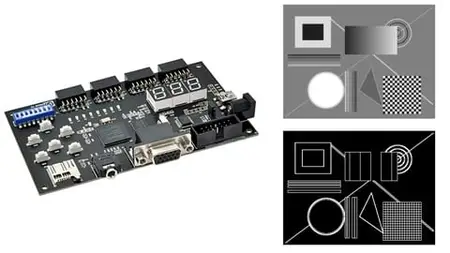

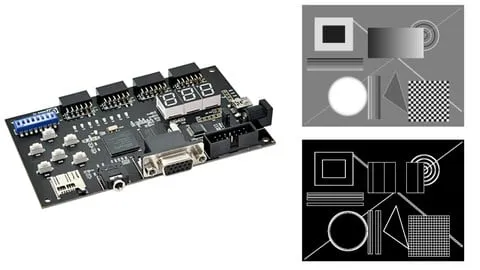

Learn Fpga Design With Vhdl : Sobel Filter Edge Detection

Published 9/2025

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 1.86 GB | Duration: 3h 59m

Published 9/2025

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 1.86 GB | Duration: 3h 59m

Understand and build an edge detector based on Sobel filter from scratch in VHDL

What you'll learn

Fundamentals of image processing and edge detection

Fundamentals of digital arithmetic and signed and unsigned manipulation with VHDL

Finite state machines

Best practices for modular, reusable, VHDL design

Architecting a hardware design and implementing in VHDL

Hands-on practical lab

Project automation with Makefile and python scripts

Requirements

Basic notions on digital electronics and VHDL are needed to get the most from this course

Description

As part of the “Learn FPGA Design with VHDL” hands-on series, this module focuses on implementing the Sobel edge-detection filter — a foundational building block for feature extraction, and image processing on FPGAs.In this course, you will:Learn image processing basicsLearn digital arithmetic basicsLearn to use the numeric_std VHDL package to manipulate signed and unsigned numbersUnderstand the Sobel operator mathematically (why does Sobel filter allows to detect edges?)Architect the Sobel filter and the edge detectorTranslate the algorithm into a hardware module in VHDLVisualize results on VGA for tests on FPGA and via memory dumps for simulationAutomate the generation of the filtered image by running a single command via Makefile and python scriptsThis engineering project is fun and will give you lot of skills in different subjects.By the end, you’ll be able to implement a Sobel edge detector in VHDL. Through this process, you will gain knowledge in image processing. You will also get accustomed to finite state machines, arithmetic on signed and unsigned numbers, RAMs and ROMs, multiplexing and hardware design in general. You will also learn to automate your project. Running all your project with one command is fun, you will gain the sight of applying it to your own projects.

Overview

Section 1: Introduction

Lecture 1 Introduction

Section 2: Image processing basics

Lecture 2 Digital image

Lecture 3 Gradient

Lecture 4 Convolution

Lecture 5 Sobel filter

Lecture 6 Edge detection steps

Section 3: Digital arithmetics basics

Lecture 7 Sign extension

Lecture 8 Binary addition - 1

Lecture 9 Binary addition - 2

Lecture 10 Binary shift

Lecture 11 Binary multiplication

Lecture 12 Binary division

Section 4: numeric_std package in VHDL

Lecture 13 numeric_std package in VHDL

Section 5: Implementing the Sobel filter in VHDL

Lecture 14 State machine of the Sobel filter

Lecture 15 VHDL implementation - 1

Lecture 16 VHDL implementation - 2

Lecture 17 Simulation

Section 6: Implementing the edge detection design

Lecture 18 Architecture of the edge detection design

Lecture 19 The memories in the design

Lecture 20 VHDL implementation - 1

Lecture 21 VHDL implementation - 2

Lecture 22 Note about VGA

Lecture 23 Project folders organisation

Lecture 24 Automating with Makefile and python

Lecture 25 Demonstration

Section 7: Conclusion

Lecture 26 Conclusion

Beginner Digital Electronics students and engineers or anyone interested in learning FPGA design