Cadence INNOVUS version 19.11.000 (ISR1) | 3.9 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled INNOVUS 19.11.000 (ISR1) is part of the broader Cadence digital and signoff suite, which provides customers with an integrated full flow, delivering a predictable path to design closure and also supports Cadence’s Intelligent System Design strategy, accelerating SoC design excellence.

Release 19.11 Overview

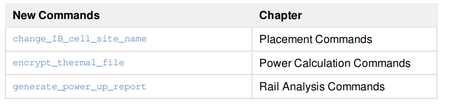

New Text Commands and Global Variables

The following table lists the commands that were added to the Innovus software in this release. The second column identifies the corresponding chapter of the Innovus Text Command Reference where the command is documented.

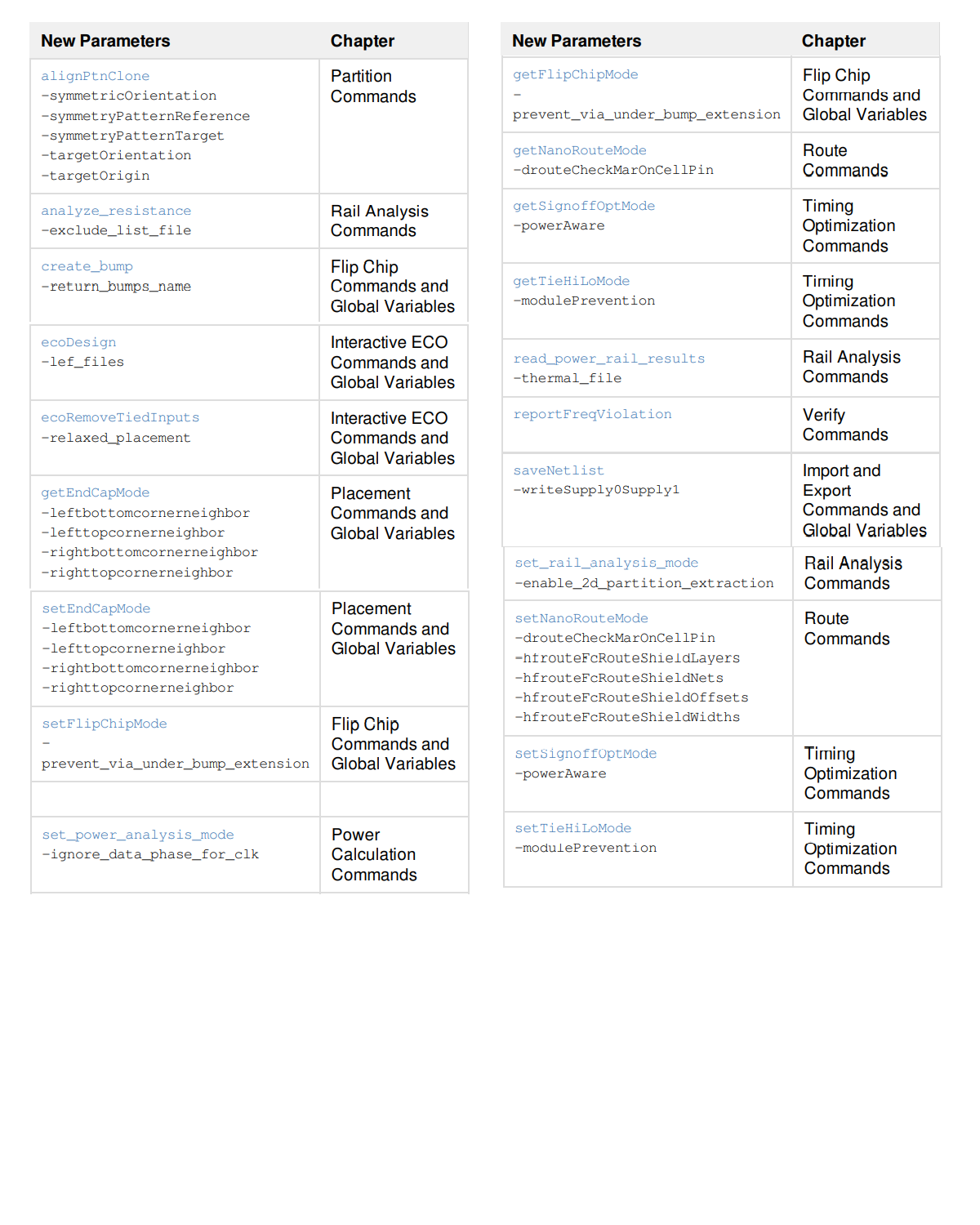

New Command Parameters

The following table lists the parameters that were added to the Innovus software in this release. The second column identifies the corresponding chapter of the Innovus Text Command Reference where the command is documented.

Obsolete Command Parameters

Supported in this Release

The following obsolete text command parameters will continue to be supported in this release, but will be removed in the next major release of the software. Update your scripts to avoid warnings and to ensure compatibility with future releases.

verifyProcessAntenna

-leffile

Use the write_lef_abstract command instead.

Removed from Software

The following obsolete text command parameters have been removed from the software.

routeDesign

-hf_clock

This parameter has not been replaced.

CCMPR02122206 Crash in read_def with 19.11

CCMPR02122181 Unable to run floorplanning

CCMPR02120749 User set timing derates are getting overwritten

CCMPR02119829 scandef errors while restoring flattened ILM DB

CCMPR02118446 Innovus 19.10 is locking up during ccopt_design CUI

CCMPR02118241 selectInst crashes in 19.11_e088

CCMPR02116891 Fatal crash during place_opt_design with Innovus 19.11-e081_1

CCMPR02115286 place_opt crashing during scheduling file restore in ECF

CCMPR02114856 Coloring is crashing at NR::sort_inst() on one of the designs

CCMPR02114633 The add_fillers command causes Innovus 19.1 to hang for customer in tapeout. Works with 18.13-s088_1.

CCMPR02113715 select_bump -net <netname> is not selecting the corresponding bumps

CCMPR02112033 SEGV on a design

CCMPR02111670 detachTerm SEGV due to user usage error

CCMPR02111184 place_opt_design -opt crashes after SKP initialization

CCMPR02110538 assignPtnPin SEGV

CCMPR02110373 optDesign got crashed at spsInstMapLLG::getContextDemandInRange

CCMPR02110294 Nanoroute creates patch wires on _SADP_FILLS_RESERVED in N5 node

CCMPR02109985 Innovus crashed in optimization during DrvOpt

CCMPR02109757 SEGV during "routeDesign -trackOpt"

CCMPR02108858 Run eGR for better congestion prediction

CCMPR02108852 Timing still jumps a lot if redo full eGR-steiner with incr-eGR-steiner on

CCMPR02108281 Innovus does not connect supply pins from apply_power_model -supply_map

CCMPR02107699 Crash at the AddStripe command

CCMPR02107624 1911 place_opt_design crash

CCMPR02107247 Early global router bad clock routing with NDR tracks defined

CCMPR02106808 fterm location changed after write_db and then read_db

CCMPR02106711 SEGV during iSpatial

CCMPR02106530 Tool crash at dbsStripBoxGroupMgr::iterator globalDetailRoute due to missing power connection in netlist

CCMPR02105917 18.13 CCOpt SEGV on "RefinePlaceCaller::ReportMovementHelper(const InstRec& instRec,"

CCMPR02105502 saveDesign crashing with 19.1-p002_1

CCMPR02105497 addEndCap crashing randomly in mixed placer flow with 19.11

CCMPR02105432 **WARN: (IMPSC-1026): Instance pin %s connects to net %s with multiple (5) drivers

CCMPR02104875 place_opt_design crash

CCMPR02104801 19.11 postcts crash before hold fixing

CCMPR02104799 19.11 report_power crash

CCMPR02104685 Innovus crash in place_opt_design 18.13 CUI

CCMPR02104677 Innovus crash with placeInstance of large delay cell

CCMPR02104565 Innovus crashing right after checkFPlan with 19.11

CCMPR02104540 Crash during routeDesign

CCMPR02104528 Bus Planning - place_opt_design adds buffers outside busGuide

CCMPR02104489 Design load crashing in 18.15

CCMPR02103946 eco_oa_design gives error in 18.14

CCMPR02103187 UPF file duplication lines on set_iso*

CCMPR02102533 Need Secondary PG connection to extend top stripe to switch cell pin

CCMPR02102523 Tool crashes during the optDesign -postCTS command

CCMPR02102514 verify_drc reports a false EOL-Keepout violation

CCMPR02102399 earlyGlobalRoute crashed due to user's incorrect -earlyGlobalMinRouteLayer setting

CCMPR02102357 Innovus is unable to generate DRC clean multicut power vias

CCMPR02102330 Power routing is not adding vias in 18.14-e070 and later

CCMPR02101742 signoffTimeDesign command is checking out two Tempus licenses when only one is required

CCMPR02101735 Tempus eco crash during drv optimziation

CCMPR02101728 Filler node crashing while executing the verifyLitho command

CCMPR02101712 Crash during global placement

CCMPR02101422 Need help on Tempus TSO tool crash during invocation of eco_opt_design -hold

CCMPR02101155 savePartition crash in 19.71-e003

CCMPR02101131 Crash during routeDesign -highFrequency

CCMPR02101005 Innovus crash with globalDetailRoute during the Route stage

CCMPR02100922 SEGV when "place_opt_design -no_pre_place_opt" from iSpatial DB

CCMPR02099805 M4 EOL keepout violations

CCMPR02099791 M2 EOL keepout violations

CCMPR02099754 Place stage in ccopt_design command crash

CCMPR02099753 routeDesign reports ERROR: NR History Map is not available in dbs

CCMPR02099708 optDesign postRoute timing difference between fullDC timing and optimization

CCMPR02099683 **ERROR: (IMPTCM-4) happens in create_proto_model

CCMPR02099655 Extraction crashes when running report_timing in 19.71-e003_1

CCMPR02099500 place_opt_design hangs after issuing **WARN: (IMPSP-9089): Feature 'LEF ROWPATTERN' is obsolete

CCMPR02099187 Utilization test - EGR correlation

CCMPR02099049 TQuantus crash inside routeDesign

CCMPR02099034 Editpowervia creates M2 Same metal aligned cut violations with cell geometries

CCMPR02098961 FC route leaving a mess for some bumps when solution seems simple

CCMPR02098657 Improve grid coarsening heuristic in line with suggestions for CCR 2089602

CCMPR02098412 routeDesign crash

CCMPR02098384 write_floorplan_script does not write out the same location for bump in tcl as create_bump -location issued

CCMPR02098318 Crash during saveDesign

CCMPR02097764 Crash during place_opt_design using 19.11

CCMPR02097660 Negative shielding ratio is being reported during the clock stage

CCMPR02097472 Innovus 171 routeDesign segmentation fault

CCMPR02096845 Very high runtime of ~36hrs for first areaReclaim call in place_opt_design

CCMPR02096512 19.11 postRoute DrvOpt NBF transform high CPU time due to forward depth 2 sub timing graph eval

CCMPR02096495 19.11 postRoute DrvOpt Resize transform high CPU time due to large sub timing graph size

CCMPR02096476 Update to latest UPF parser (d016)

CCMPR02095873 SEGV Crash at refine place after DRV optimization

CCMPR02095823 Incorrect consideration for top and bottom rects of standard via variant

CCMPR02095681 optDesign utilizes incorrect MBFF cells from library binding in MSV design

CCMPR02095557 optDesign -postCTS crashes with 18.14-e058_1

CCMPR02095543 Fatal ERROR when trying to run ecoAddRepeater

CCMPR02095542 ecoRoute not called after refine place within postroute opt

CCMPR02095007 When using ORIENT syntax to TLEF, layer via is ignored in IMPLF-420

CCMPR02094945 SEGV during place initial on a design

CCMPR02094940 ecoRoute not fixing via0 violations

CCMPR02094916 NanoRoute: further improvement on fixing false EOL and trim violations

CCMPR02094830 Crash during routeDesign -trackOpt

CCMPR02094692 Innovus crashing while running the ecoAddRepeater command

CCMPR02094140 assignPtnPin SEGV

CCMPR02094112 Restricted size-only constraint not honored for some cases during preCTS optimization

CCMPR02094063 SEGV during place_opt_design -phys_syn

CCMPR02094036 CUI equivalent of legacy command setNanoRouteMode -drouteCheckMarOnCellPin

CCMPR02093958 Pins not aligning with align pin. Choosing closer edge rather than aligning

CCMPR02093491 flip_chip_router causes SEGV using 19.11-e044_1

CCMPR02093320 addStripe failed to create M4 PG stripes cross the whole core area correctly

CCMPR02092585 SaveDesign Error out with **ERROR: (IMPSYC-1919)**

CCMPR02092437 Routing runtime not competitive

CCMPR02092108 MBF mapping file is incorrect after split

CCMPR02092095 Crash during routeDesign in a design

CCMPR02091794 Incorrect delay calculation in IO PG lib

CCMPR02091657 SEGV during ecoRoute - Extracting RC

CCMPR02091577 ccopt_design continues to leave transition violations

CCMPR02091559 Nanoroute crashes when loading APA file

CCMPR02091370 SEGV during extractRC in postroute top-level DB

CCMPR02091063 Bug fix for pgFill -fixIsoVia support

CCMPR02090673 SEGV during route

CCMPR02090323 Innovus 19.1 Crash during place_opt

CCMPR02090170 Crash during the placeopt stage when customer is trying custom buffering

CCMPR02089616 Passive fill generates DRC violations

CCMPR02089524 19.11: postRoute TNS opt NBF CPU time is high comparing to other transform due to too many legal loc check

CCMPR02089507 read_parasitics failing to read its own written rcdb file under routeDesign -trackOpt

CCMPR02089402 Crash in delay calculation in optDesign -postRoute

CCMPR02089181 WidthTable Violation

CCMPR02089048 Macro poly DRC violation in mixed mode

CCMPR02088394 Innovus 19.11-e024_1 First ecoRoute in optDesign -postRoute has SEGV

CCMPR02088301 19.11: Too many refinePlace were called even no non-legal commit during optimization in postroute opt

CCMPR02088217 "Non-pin * cannot be skew_group sink" messages related to multibit flops during ccopt_design

CCMPR02087923 postCTS hold fixing crashes with SEGV

CCMPR02087717 Crash during eco Implementation

CCMPR02087647 globalDetailRoute SEGV while restoring pin access data from .apa file

CCMPR02087294 saveDesign crashes after postroute optimization with the ILM-based flow

CCMPR02087027 Make passivation layer independent to other layers

CCMPR02086273 Innovus 1801 output has -update {} and -supply {} which make the output unreadable

CCMPR02086023 GUI hang after gui_highlight gui_show

CCMPR02085574 GUI display speed status will auto change

CCMPR02085341 Nanoroute does not appear to be using METALWIDTHVIAMAP for MUSTJOIN connections

CCMPR02085302 chip_top "ecoRoute" stuck for 15hrs at a step of marking dirty area

CCMPR02085254 Enhancement request to elaborate the path groups in the timeDesign summary

CCMPR02085242 IMM crash in 19.11e036

CCMPR02084614 Crash during ccopt_design -cts

CCMPR02084601 NR leaving mustjoin pins disconnected

CCMPR02084589 Off Trim Grid Vioation

CCMPR02084571 19.11: Hold don't touch marking is taking long time

CCMPR02084455 Crash observed during saveDesign

CCMPR02084341 Crash during eco commands

CCMPR02084324 SMAC violation after postRoute pg hook-up

CCMPR02083810 19.11 SEGV at esiDcalc::createMultiDrvTask

CCMPR02083788 AssignIOPin not assigning clock pin with ECF

CCMPR02083751 pgFill -fix_iso_via crashes with multicpu

CCMPR02083393 Post-route optimization tool crash

CCMPR02083234 Innovus apply_port_map does not reconnect ports connected to constants

CCMPR02083132 Support halo placement for "even height" block sizes

CCMPR02082651 freeDesign does not clear via information by add_via_definition

CCMPR02082510 Multi-Bit cells not being inferred by Innovus

CCMPR02082402 addRing fails with IMPPP-4051 if the ring is generated to align with block boundary

CCMPR02082146 18.14: place_opt_design with early clock flow SEGV

CCMPR02082039 19.11 crash during ccopt_design -check_prerequisites

CCMPR02081781 Tool crashes during oaIn

CCMPR02081636 place_opt_design crash in optDesign phase

CCMPR02081585 18.1/19.1 scanTrace after place_opt_design gives warn of IMPSC-1151

CCMPR02081556 end_parallel_edit comes out with SEGV

CCMPR02081382 HardenOpt is taking 40 minutes without any commit in postroute opt

CCMPR02081292 18.1/19.1 scanTrace gives warn 1138 if run twice

CCMPR02081233 Crash reported during saveDesign in the floorplan stage

CCMPR02080914 Tool crash running verifyPowerDomain

CCMPR02080803 There was a short between M2 two pins of a cell placed next to the PG stripe

CCMPR02080792 The field "pin group" is not updated automatically in pin Editor

CCMPR02080777 Trim to trim spacing violation

CCMPR02080736 Missing inserted routing trim on top of pre-defined cell trim OBS

CCMPR02080717 Crash during oaIn with different cell name with design cell

CCMPR02080455 Need improvement for total fullDC runtime

CCMPR02080369 NRHF crash while routing 6K nets

CCMPR02079728 New off trim grid violations with NR

CCMPR02079659 Enhance moderate PG via insertion to align vias instead of using checkboard pattern

CCMPR02079374 NRHF crash ExportRipin

CCMPR02079337 Tie cell addition fails for many pins after taking 15+ hours, keep on applying GNCs in loop

CCMPR02078612 tQuantus is not honoring layer based RC scaling on SEC10

CCMPR02078459 summaryReport -outDir does not output all files into the specified outdir

CCMPR02078420 addStripe with stapling style will not generate full expected for M4 in channel

CCMPR02078095 Innovus not able to support CPF input/ouput_domain options in create_level_shifter_rule

CCMPR02078075 place_opt_design uses wrong clock_latency value

CCMPR02077863 Unacceptable CTS memory/runtime tracing a macro with complex internal structure

CCMPR02077830 Manual ICG sizing leads to better postCTS QoR compared to default skewClock sizing

CCMPR02077823 ccopt_design error out with "MT ERROR" messages

CCMPR02077284 apply_power_model -port_map not making connections

CCMPR02077263 setTopCell command is crashing when invoked from GUI

CCMPR02077202 Incorrect mbit naming by Innovus causing NEQs in LEC

CCMPR02077100 Need Max Layer control for Shield tapping

CCMPR02077099 place_opt_design crash with 19.11

CCMPR02076922 Sspecial-via search box too small when considering altered pre-existing metal-shapes. Leads to drc errors

CCMPR02076860 Need GUI enhancement for adding zoomTo -radius option

CCMPR02076566 CCOpt Halos not being applied to clock roots

CCMPR02076515 M2 EOL violation not flagged by verify_drc

CCMPR02076308 19.1 qor degradation when compared to 18.12

CCMPR02076247 VIA2 spacing violations within Invs18.14

CCMPR02076112 Innovus does not connect supply nets properly when apply_power_model is used

CCMPR02076099 saveDesign cannot override the starting DBS when setOaxMode -locking true

CCMPR02075993 M1 shorts seen during Nano route

CCMPR02075786 verifyConnectivity detects open error at net accessing pins as feedthrough

CCMPR02075746 Large increatse in routing DRCs when enabling passive fill

CCMPR02075577 trimDesign getting stuck in Innovus 19.10-b706_1

CCMPR02075445 Power bump routing using fcroute

CCMPR02075429 Massive detour for a net on critical path

CCMPR02075313 One pass run with preCTS useful skew run progress is very slow

CCMPR02075239 ecoRoute in distributed mode flags false adjacent cut violations not seen in non-distributed mode

CCMPR02075160 Dangling wires left after ecoRoute in 18.14_e043_1

CCMPR02075154 Crash while NR starts routing of the clock nets during ccopt_design

CCMPR02074980 fcroute shorts and opens

CCMPR02074966 fcroute taps wrong VSSO pin

CCMPR02074539 18.11-s100_1 crash when running "get_lib_clock_tree_path_delay"

CCMPR02074460 M1 routing under X1 trim layer

CCMPR02074300 ccopt_design hang during clustering

CCMPR02074069 addStripe causing segmentation fault when "-power_domains" is specified

CCMPR02073996 19.10 routeDesign 30% peak memory degradation compared to 18.12

CCMPR02073717 Pin access analysis takes 7 hours in one cell

CCMPR02073681 NRHF crash, CheckPinAccess

CCMPR02073600 Innovus gets confused about colors when importing from display.drf

CCMPR02073498 Huge DRC jump at the end of optDesign -postRoute

CCMPR02073423 CTD SEGV selecting Constraints - dont touch on clock mesh design

CCMPR02073380 delete_dangling_port introduce error IMPSYC-1919

CCMPR02073245 SEGV during route_secondary_pg_pins in timing_driven

CCMPR02073054 _SADP_FILLS_RESERVED is written to Netlist

CCMPR02072973 checkPlace/place_opt_design reporting false pin access violations

CCMPR02072971 DIAG in 18.13-s088_1

CCMPR02072915 place_opt_design not honoring selective sizeonly for all the specified instances

CCMPR02072913 Incorrect error message for 'addStripe -power_domains' and inconsistent behavior between multi/single PD

CCMPR02072886 trackOpt seeing very optimistic timing compared to postRouteOpt - 90nm

CCMPR02072858 addStripe creates euclidean spacing violations to 45-degree edges of bumps

CCMPR02072754 Missing VIA definition in DEF

CCMPR02072685 ERROR: (internal Tcl error) 'invalid command name "cbGet"

CCMPR02072464 This switch "-usePostCTSHighFanoutNetFixing" is still leaving some HFN unfixed during postcts

CCMPR02072308 Slack changes after reset_path_group

CCMPR02072224 User gets repeatable stack trace when selecting an IO pad

CCMPR02072197 editAddRoute does not honor assign multi pattern color

CCMPR02072146 place_opt_design crash

CCMPR02071689 Innovus 1801 3.0: invalid command name "::MSV_UPF::define_power_model"

CCMPR02071682 addTieHiLo creates a new net with empty props

CCMPR02071594 FlexILM for blocks does not show partition pins in Hierarchical DB when block pins have PLACED status.

CCMPR02071430 ICG pin alignment not having pins aligned

CCMPR02071161 SEGV during saveDesign in 19.10-b706_1

CCMPR02071129 Wire spreading causes lots of DRC in "LEF58_EOLEXTENSIONSPACING"

CCMPR02070901 19.1 code bash: routeDesign left more than 1000 DRCs on M3/M4 in 19.1 compared to 18.1

CCMPR02070851 PSW enable In/Out pin are not in ALWAYS ON power domain

CCMPR02070822 Miss out PA violation Hybrid row flow

CCMPR02070754 Seeing NRDB-671 warning that PG nets are not routed in 19.10-b706

CCMPR02070725 Router hang on a testcase

CCMPR02070681 SEGV during timing optimization under power reclaim

CCMPR02069894 Star router using 19.11-e010 results in 44 opens where it can be resolved manually

CCMPR02069870 fixCellEMViolation can NOT fix all violation due to NoViewFound ERROR reason

CCMPR02069867 deleteFiller -inst print out messages for each deleted filler cells

CCMPR02069497 Crash during optDesign -postRoute on chip level

CCMPR02069357 addRepeaterByRule is not buffering some nets

CCMPR02069314 report_metric should use the id itself as a tag name while comparing multiple metrics instead of "G" "T1"

CCMPR02069267 ECF not able to identify all ICGs with multi driver net

CCMPR02069237 Large TAT and memory jump during postCtsHold due to high fanout net from place_opt

CCMPR02069186 UseMultiCutViaEffort hard - Huge runtime and DRC viols because NR does not use appropriate VIA12 vias

CCMPR02069052 Problem of memory in deleteRouteBlk

CCMPR02069016 skewClock should support ICG sizing having ICG clock pins connected to multi driven net

CCMPR02068981 place_opt_design -place takes longer runtime during global placement

CCMPR02068863 ccopt_design should accept ILM model type "SI" and just use the data it needs

CCMPR02068721 CCOPT crash in cell filtering

CCMPR02068527 delete_assign issues false warning since no new instance/net are created

CCMPR02068257 Crash during ecoRoute for FE Block

CCMPR02068186 optDesign is coming out with illegal placement

CCMPR02068129 Stack trace a flattenPartition

CCMPR02068105 via pillars create short with M2 cell blockage

CCMPR02068057 refinePlace hanging again, not finding legal locations for cells due to "Other"

CCMPR02068045 'colorizePowerMesh' crashed with 18.14-e033_1

CCMPR02067999 Stack trace during DRV optimization at Postroute

CCMPR02067997 Innovus route stage end up with many un-routed (open net)

CCMPR02067401 Very long runtime of global route during ecoRoute

CCMPR02067384 displayScanChain does not work in an interactive session

CCMPR02067381 Unnecessary jogs during FlexH routing

CCMPR02066879 reportVtInstCount is giving stack trace

CCMPR02066708 High Runtime during detail route

CCMPR02066646 Sizing in "skewClock -postRoute" is not honoring "set_ccopt_property buffer_cells { ..} -clock_tree"

CCMPR02066621 NanoRoute leaves fixable Cut Short violations

CCMPR02066461 Runtime consumed by checking antenna on constant nets

CCMPR02066079 Routing DRC caused by via pillars during postRoute Opt

CCMPR02066026 Stack trace at the start of Postroute while restoring markers from Route Db

CCMPR02065956 Checkplace reports false TPO violations after filler insertion

CCMPR02065949 Secondary PG for merged nwell ignores some un-connected pins (with log message)

CCMPR02065944 SEGV on IMPSP-2031 error message during place_connected

CCMPR02065885 Tool hangs at the gen_net of droute during via pillar insertion

CCMPR02065879 18.13e070 exits with synthesize_flexible_htrees command without completing htree routes, errors with 18.13e050

CCMPR02065638 Innovus false forbidden spacing My.S.27 violation

CCMPR02065573 Crash in top-level postcts_hold (ilm design)

CCMPR02065317 Route hangs

CCMPR02065062 Fail to route net in region. Set net to open

CCMPR02065046 Target-based Opt file has parsing error with bit slice name

CCMPR02064996 ccopt_design -cts stage crashes during the clustering stage

CCMPR02064583 ccopt_design hangs

CCMPR02064372 Detail routing initial DRC count is very high without the option '-routeEcoOnlyInLayers'

CCMPR02064336 Issues when importing Virtuoso colors into Innovus

CCMPR02064293 place_connected not placing ICG close to macro

CCMPR02064292 Antenna diodes placed in incorrect power domain during routeDesign

CCMPR02064190 verify_drc segfaults with 18.1x

CCMPR02064153 pdzgSetNbInfoMC() SEGV.

CCMPR02063566 signoff extraction is not working in 18.13 & 17.16 - same scripts worked OK in 17.15

CCMPR02063550 route_details is resulting in false trim OBS short violations

CCMPR02063543 SEGV during editPowerVia

CCMPR02063528 NR is reporting off trim grid violations that are not real

CCMPR02063420 Error while restoring the design

CCMPR02063403 Crash in Global Placement

CCMPR02063022 OPT uses much less via pillars when cut class for STACKVIARULE is not defined in rule LEF

CCMPR02062972 1801 produces error IMPDB-1207 when supply set is not fully defined before apply_power_model

CCMPR02062862 Long runtime of "editDelete -net" command

CCMPR02062538 NanoRoute SEGV

CCMPR02062475 17.1 & 18.1: Crash in post-route opt (CCOpt) from coePostCommitDelayUpdater / CompressedWave, ground voltage is not 0

CCMPR02062301 Buffering issue due to Iso cells missing in Innovus Stylus

CCMPR02062186 ecoRoute stops with #ERROR (NRDB-158) Missing via

CCMPR02061999 SEGV while doing GUI edits

CCMPR02061944 addFiller not able to insert double height cell

CCMPR02061900 SEC10 preRoute extraction miscorrelation

CCMPR02061887 addStripe breaks stripe at selected even when -break_at set to none when power domains exist in design

CCMPR02061828 Secondary PG pin routing setup does not get saved when Tie cells are not part of Prects Db

CCMPR02061821 Still difference between timing seen by optimization and timing command

CCMPR02061152 mesh_vias are not added on the top/bottom 2 rows

CCMPR02061150 Sstack trace generated during check_design

CCMPR02061038 Core dumped at ediPowerVia

CCMPR02060787 Attribute editor should have the editChangeNet -to <net_name> GUI enhancement

CCMPR02060716 Stack trace while saving OA design after Routing (Stylus)

CCMPR02060711 Enhancement to enforce row numbers in block and between macros to be multiples of 4

CCMPR02060651 N/A reported in Expanded views if "ignorePathGroupsForHold {in2reg reg2out in2out default}" specified w/o creating the path group

CCMPR02060537 Add new option "-specify_cut_class" for user to specify cut class by cut layer

CCMPR02060307 ccopt_design crashes

CCMPR02060288 CTS HTree crash

CCMPR02060249 4 chip_top "optDesign -postRoute -drv" long runtime

CCMPR02060219 Huge runtime during macro checker

CCMPR02060201 Innovus is crashing during ecoRoute

CCMPR02060195 Global skew and band occupancy sometimes broken by late stage CTS

CCMPR02060125 update_power_vias does not respect via11 blockage over m10 block pins but does over m10 stripes

CCMPR02060072 Inverting ICG scoring function too restrictive (follow on from CCR 1969990)

CCMPR02060054 Attribute editor window or any GUI box should be closed with one bind key preferably "esc"

CCMPR02059995 Wrong design name saved in *.enc.dat/gui_pref.tcl

CCMPR02059816 set_visible_nets does not work in hierarchy db

CCMPR02059756 Inconsistent report between budget and justify on port with case

CCMPR02059644 ecoChangeCell in batch mode SEGV

CCMPR02059633 addTieHiLo breaks logical equivalency, module based

CCMPR02059562 Wire gets dropped when writing OA db and reloading

CCMPR02059548 create_snapshot on restored placeopt DB creates massive timing in GPU block

CCMPR02059547 checkPlace taking 4-7hrs on a routed design

CCMPR02059434 Floorplan prediction in Genus calling Innovus 'planDesign' results in SEGV

CCMPR02059411 sroute SEGV during stripegen target

CCMPR02059223 congRepair QoR issue when restart new Innovus section

CCMPR02059140 Innovus fails to optimize critical io group timing with high effort and weight

CCMPR02059053 addRepeaterByRule SEGV

CCMPR02058952 sroute moving ports in COVER status to outside the die

CCMPR02058873 Need to issue a warning message related to tech file error

CCMPR02058738 Innovus crashing during CTS when using nested fences and the dont_touch_hports attributes after issuing IMPCCOPT-4283

CCMPR02058346 Need to improve initial timing QoR after NR

CCMPR02058291 Stack trace during addWellTap in 18.12 and 18.13

CCMPR02058200 [CPU][NY] Crash after deleting a net

CCMPR02057772 DIAG [dbWireIO.c:1562:dbiNetNotNeedToSave] during saveDesign

CCMPR02057589 NR/Swapping vias does not respect hard NDR spacing besides verify_drc cannot detect the errors

CCMPR02057557 Clock route jogging on preferred routing layers using 18.14

CCMPR02057549 create_clock_tree_spec output file has typo

CCMPR02057514 Crash during global routing part of routeDesign

CCMPR02057474 Manual swapping of ICG improves REG2ICG paths in postcts

CCMPR02056789 dbget changes deleteFiller behavior

CCMPR02056738 appending empty lef file list to init_lef_file causes saveDesign link every file in the current run dir

CCMPR02056633 Innovus crashing on SARC design during QRC extraction

CCMPR02056023 Does setEcoMode -LEQCheck true affect ecoAddRepeater honoring location parameter

CCMPR02056011 savePartition with upf should handle inverted control signal

CCMPR02055978 Crash during save design after refreshing upf, need freeTimingGraph

CCMPR02055314 Clean up of DIAG messages during preroute extraction due to missing vias in LEF

CCMPR02055297 Early global route crossing partition boundary at two locations

CCMPR02055226 PostRoute optDesign crashed during ecoRoute detailRoute

CCMPR02055209 routeDesign -highFrequency SEGV

CCMPR02055104 add_gui_shape or addCustomBox no longer allows user to manually resize using GUI due to failed of setObjFPlanBox

CCMPR02055067 18.13-e070_1 and 18.14 set is_memory to true even for all std cells when voltage scaling lib set is loaded

CCMPR02054834 Huge amount of Clock ID degradation is observed during egrpc

CCMPR02054599 SpecifyCellEdgeSpacing -underPG does not work as suggested

CCMPR02054412 assignTSV takes huge runtime with large number of front bumps

CCMPR02054352 Order of columns not matching rows

CCMPR02054161 Innovus shows random behaviour in optDesign -postRoute -setup -hold, in one run crashes during hold optimization

CCMPR02054105 Crash during placeDesign command

CCMPR02053999 Fix memory leakage for trimMetalFillNearNet

CCMPR02053765 OA DB Checker cannot consider standardViaVariant correctly

CCMPR02053080 CTS crashing at clustering with 17.15 version

CCMPR02052825 SEGV when do place_opt_design

CCMPR02052490 HUGE run time is seen while implementing the PG MESH

CCMPR02051947 SEGV in post-cts opt in ccopt_design after area reclaim

CCMPR02051261 Back-and-forth buffering observed due to partitioning by UPF logical power domains

CCMPR02050741 Flip chip router with star algorithm v19.1 results in corrupted routing path data message in a multi pad to bump design

CCMPR02050703 Flexible htree image colormap change makes the data difficult to use

CCMPR02050480 Timing miscorrelation moving from tQuantus to iQuantus

CCMPR02050031 Htree net routed with min cut DRCs

CCMPR02049947 NR is not updating the default power domain dimension after switching partition

CCMPR02049946 add_stripe misses via on one of the macro power pins

CCMPR02049627 fixVia -minstep DIAG issue caused by FGC false report drc

CCMPR02049322 Mfill cap not being extracted correctly for tQuantus

CCMPR02049229 Provide an option to allow floating pins to be placed at abutted edge BUT NOT abutting to other floating

CCMPR02049164 Request to remove escape character in instance name for "create_inst -inst"

CCMPR02048374 setDesignMode -node S5 causes huge jump in eGR congestion

CCMPR02048344 Strange routeDesign -wireOpt behavior

CCMPR02047828 egr misscorrelation with NanoRoute

CCMPR02047608 Long clock runtime for the block

CCMPR02047048 streamOut: wrong min/max voltage text labels for 45-degree shapes

CCMPR02046629 remove_assigns -net is removing assign statements on all the nets in the design

CCMPR02046466 NanoRoute: further improvement on fixing trim grid violations is needed for certification

CCMPR02046325 Tran violations reported with report_constraint and reportTranViolation have mismatch in postRoute

CCMPR02046088 DIAG during create_timing_budget

CCMPR02045997 saveNetlist creates wrong assign statement for the input port

CCMPR02045919 When stretching or changing origin of partition, pins get moved outside of partition and off-track

CCMPR02045849 Not able to build clock tree with in-bound cells

CCMPR02045829 add_stripes hung for longtime

CCMPR02045621 Horizontal max length violations are not being fixed by tool

CCMPR02045449 editPowerVia - same mask metal aligned cuts

CCMPR02045272 Floorplan file saved with saveDesign is missing area-IO instances

CCMPR02044918 Innovus should skip any IO cell when collecting domain tech site

CCMPR02044551 16nm power via array generated with insufficient space between cuts

CCMPR02044541 '-optimizeFF true' for Hold is degrading DRV on both data and clock

CCMPR02043881 Crash and DIAG Assert "peIsDesignExtracted() && peiExtStatus" after tQuantus RC extraction

CCMPR02043363 Map -noapplycpfrule option in CUI and make it public to add_power_switch both in CUI and Legacy

CCMPR02043269 ecoAddRepeater missing detail warning message if using -net versus -term

CCMPR02043233 Why top critical net is not layer assigned at place_opt compared to clock?

CCMPR02043217 ccopt_design removing pre-routed routing

CCMPR02042583 ecoRoute crashing after restoreDesign -noTiming

CCMPR02042544 ecoAddRepeater -hinstGuide executed with setEcoMode -batchMode false

CCMPR02042506 40nm add/check_metal_fill SEGV

CCMPR02041798 write_power_intent -1801 is taking longer than expected to dump out upf

CCMPR02041690 Need a message when tool replaces max input delay by min value

CCMPR02041649 Placer needs to align placement of insts with M3 via pillars wrt M3 PG

CCMPR02041585 Timing Debugger generates hold data instead of setup data when timing_analysis_check_type is set to hold

CCMPR02040999 Module function not preserved after place_opt_design -opt

CCMPR02040993 **ERROR: (IMPESI-3201): Delay calculation failed for net and causing SEGV

CCMPR02040333 Power grid insertion to support RIGHTWAYONGRIDONLY EXCEPTWIDTH

CCMPR02040038 IQRC does not see physical connectivity between terminal wire segment (IMPEXT-1392)

CCMPR02039519 CCOPT SEGV during refine Place

CCMPR02039062 NR leaves many open nets when access macro pin in a region

CCMPR02038277 checkPlace issues pin access warnings and violations while router is able to route

CCMPR02038152 Router is crashing during hotspot fixing in Pattern matching flow

CCMPR02038098 Pin legality issue causing PG shorts

CCMPR02037494 Power hookup not happening for always on buffer while using add_port_driver

CCMPR02037177 AddTieHiLo adding a cell per pin instead of a cell for multiple pins

CCMPR02036952 Re-generate .apa file automatically if moved or deleted in the previous DB

CCMPR02036922 globalDetailRoute -selected SEGV

CCMPR02036415 MIX_PLACER - the PG modeling for stdcell placement is too pessimistic

CCMPR02036375 [invs] write_floorplan_script command dumps out reg's [string] index without curly braces

CCMPR02036227 Layer preference not honored for special clock routing with the route_ccopt_clock_tree_nets command

CCMPR02035281 Request to enhance S20 std cell pin access routing

CCMPR02035102 addFiller creates edge spacing violations

CCMPR02034883 Stacked vias not added when THICK_CU_D with is between 2.0 and 2.1

CCMPR02034653 Filler insertion on placed db leaves gaps and checkPlace DRCs after filler cell insertion

CCMPR02034353 Powerplan via gen needs to support new CUTCLASS orientation syntax

CCMPR02033663 Vague errors on reading the same CPF after free_power_intent

CCMPR02033400 verify_drc does not report violations between stripes and 45-degree bump shapes

CCMPR02033327 place_opt_design hang with Invs 18.12 and 18.13

CCMPR02033107 Non-determinism in FDS

CCMPR02032826 Need routing halo to behave as a hard constraint and apply to stdcells as well

CCMPR02032364 tQuantus vs signoff_Quantus is not good

CCMPR02031913 postRoute optDesign makes lots of fixable color violations

CCMPR02031404 Utilization not competitive

CCMPR02031150 Partitioning not saving NDR track name to partition's floorplan file

CCMPR02029175 Improve PRO TAT on large designs (Adaptive EcoRoute Flow)

CCMPR02028415 Enhance write_lef_abstract to create minimum spacing cut out for non-rectangular pin

CCMPR02027822 report_path_group_options fails to report -early options

CCMPR02026581 For Design having ILM create_clock_tree_spec generates 56ns early-tapping on 1 ilm reg clk pin

CCMPR02026253 Filler cell vertical stack issue

CCMPR02026031 Observing new zigzag routes with ccoptDesign -cts

CCMPR02025887 The reportCapViolation -all -min command is not detecting min cap violation on port

CCMPR02025657 Bug against NR_DRC to not treat trim bridging 2 disjoint wires(pins in this case)

CCMPR02025200 Automatic via tuning at addStripe could avoid missing vias

CCMPR02025054 Via blockage and checker function enhancement

CCMPR02024232 Forbidden spacing issues seen after detail routing

CCMPR02024132 Clock routing creates stubs on few nets causing EM violations

CCMPR02023492 NDR violations on M5(6) for via_pillar

CCMPR02023456 Crash in msvConnectAlwaysOnPowerGround during place_opt_design

CCMPR02023431 Fill1 gap between MBFF and tap cells

CCMPR02022973 SAI create_module -gateCount to specify the entire stdcell area not just the flexfiller area

CCMPR02022953 2x2 TVDD pin via pillar insertion

CCMPR02022504 Insertion delay due to suboptimal tap assignment

CCMPR02022480 Shorts during tapering for wide wires

CCMPR02022275 Lingering 7nm stacked via/MAXCELLEXTENSION issues

CCMPR02021752 Netlist check failure due to scan chain reorder on chain with macros

CCMPR02021331 optDesign -postRoute overlooks max_tran violation net

CCMPR02020831 NRHF routing outside boundary in case no DRC clean path is available

CCMPR02019093 routeDesign does not honor hard busGuide

CCMPR02018941 CCopt flexible h-tree drivers placed too close to each other (not honoring cell padding)

CCMPR02018281 Enhancement to allow addWellTap and other physical placement tools to allow EEQ capability

CCMPR02017697 CCOpt stuck at the netlist update

CCMPR02016957 SEGV during clock implementation routing

CCMPR02016716 ecoRoute fails because of nonexistent segment in PASS layer

CCMPR02016517 Lack of DRV fixing on N7 top level with INVS 18.11 (unexpected behavior of spGetBoxDemandAndSupply)

CCMPR02015149 Gigaopt post-eco mode is not running after final area recovery in 18.12-e079_1

CCMPR02013494 ARR does not add buffers in balanced mode

CCMPR02012390 Customer wants Innovus to achieve ~179mW of total power Vs current ~200mW for a 1M std-cell only design

CCMPR02012103 ERROR: (IMPVL-325) in ILM flow when an abstract (LEF) of a submodule is available

CCMPR02011414 Improve eGR runtime on large designs

CCMPR02007468 Too many hold fixing buffers getting added

CCMPR02006782 verify_drc needs to ignore NUT check on M1 layer

CCMPR02006567 N12, false litho halo violations seen by NanoRoute, 18.11

CCMPR02005032 Need Innovus to natively fix isolated via violations

CCMPR02004569 Flightline for rectilinear fences should point to the center of it rather than center of rectangle box

CCMPR02004466 Command eco_design to support -lef_files option

CCMPR02003347 route_eco/route_eco -fix_drc leaving 20-30 M1 trim2trim spacing violation in 18.12 builds

CCMPR01999519 H-tree bottom up pass did not converge

CCMPR01994813 Inconsistency in postRoute Opt (2nd PRO removal)

CCMPR01988788 Innovus fixes 300K max_trans in 25 hrs, and it hangs for 18 hours for 1st round fix, without increment info

CCMPR01982274 New feature to remove tied inputs not working as expected during optimization

CCMPR01975052 40x improvement in TNS after "place_opt -incr". Improved placement and use of faster buffers

CCMPR01972186 MAR on fixed VIA when route_eco

CCMPR01969151 Huge timing difference reported after running extractRc followed with report_timing in innovus

CCMPR01968874 nrtdGetNetRoutingLayers at huge timing QoR difference between full flow and split flow

CCMPR01966289 CNOD Optimization in placement

CCMPR01965080 report_ccopt_cell_halo_violations should output violation report for Violation Browser

CCMPR01962428 Virtuoso registry file out-of-sync with other Cadence tools

CCMPR01955769 reportShield changes shield ratio values without actual change to shielding

CCMPR01948207 Partitioning is wrongly removing rows at the top-level/inside partitions

CCMPR01943689 Innovus adding shield nets between PG and clock routes

CCMPR01932175 CCOpt run time degradation due to timing graph updates

CCMPR01928397 addRoutingHalo fail for PAD

CCMPR01925270 18.1 place_opt_design resulting in 80% more runtime compared to 17.14

CCMPR01922769 Current being incorrectly distributed between primary ground pin and bulk ground pin

CCMPR01889342 verifyPowerVia command is flagging missing vias where cell blockage located

CCMPR01867794 Placement grid violations are seen in case of nested partitions of mix track libs

CCMPR01859285 Stacktrace during writing timing model

CCMPR01835601 verify_drc detects false NSMetal violations on the RDL

CCMPR01758160 dbiSnapCoordToTrackCmd ptnSnapCoordToTrack API is not snapping to next Mask1 rather than nearest track

================================================

CCRs Fixed in Release 19.1 RTM

================================================

CCMPR02055052 Support UPF3.0 Parser

CCMPR02051505 setEdit(inn1625) vs setEditMode(inn1812) compatibility

CCMPR02051463 get_ccopt_skew_group_delay crashed

CCMPR02049931 place_opt_design crashes with "set_limited_access_feature FlipFlopMergeAndSplit false"

CCMPR02048344 Strange routeDesign -wireOpt behavior in 19.10

CCMPR02046944 SEGV during assign_clock_tree_source_groups for a design with preserved ports v19.10-d235_1

CCMPR02044791 Wire edit commands add redundant floating VIA10

CCMPR02043082 Push partition_push_network is too slow with power_intent

CCMPR02040212 legalizePin issues IMPPTN-562 warning with strange coordinates

CCMPR02040038 IQRC does not see physical connectivity between terminal wire segment (IMPEXT-1392)

CCMPR02039773 SEGV crashing optDesign at post_route during delay calculation

CCMPR02039687 Position based net connection in instance after assembleDesign

CCMPR02039644 routeDesign crash with setNanoRouteMode -routeWithTimingDriven true

CCMPR02039141 editPowerVia command to add power vias from M3 to M1 rails takes long time to complete

CCMPR02039084 ColorizePowerMesh hangs for long time

CCMPR02038227 Filler node is crashing while executing the verifyLitho command

CCMPR02038189 delete_constant_nets (deleteDangling1b1Or0s) does not respect dont_touch_hports

CCMPR02037672 addRepeaterByRule crashes after using "free_power_intent"

CCMPR02037525 NanoRoute not routing straight shots on same metal layer well

CCMPR02036862 Please map legacy setViaGenMode -ignore_design_boundary to Stylus

CCMPR02036858 Add *.enc to filetype pull down menu when using "Restore Design" in the GUI

CCMPR02036850 Long runtime of the partition command

CCMPR02036828 NanoRoute crash in 18.11, critical design

CCMPR02036805 Crash during defIn command

CCMPR02036535 tQuantus TCAP/XCAP optimism Vs iQuantus in 18.12

CCMPR02036318 postcts SEGVs with cdcc14CompressedWave5reset

CCMPR02035579 Text box size from OA design become very large in Innovus

CCMPR02035291 Got a crash when place_opt_design ran

CCMPR02033930 checkPlace struck after placement in Innovus 18.11

CCMPR02033257 Error: IMPCCOPT-1337 during the synthesize_ccopt_flexible_htrees command

CCMPR02032764 Virtual connects appear to have incorrect coordinates

CCMPR02032636 place_opt -opt SEGVs with malformed bucket chain in Tcl_DeleteHashEntry

CCMPR02031696 Error IMPVB-23 while loading Calibre PM rdb file in Innovus

CCMPR02031656 The summaryReport "Layer … Information" header string is not getting reset between layers

CCMPR02031489 Tool is crashing during the detailRoute -fix_drc in the filler node step

CCMPR02031459 postCTS optimization SEGVs during delay calculation with cdcc14CompressedWave5resetEv

CCMPR02030914 Innovus crash when clicking letter R from schematic view

CCMPR02029817 EDI writes UPF with a syntax error

CCMPR02028956 postroute opt SEGVs in initial delay calculation

CCMPR02027675 Placement crash caused by fake term

CCMPR02026908 NR creates voltage spacing violations with negative bias nets

CCMPR02026480 synthesize_ccopt_flexible_htrees runs out of memory at "Computing placement data …"

CCMPR02025889 get_db returns invalid values for the attribute .bbox.dx

CCMPR02025882 SEGV during diode insertion for antenna fixes

CCMPR02025643 IMPCK-1021 on a three-metal layer design

CCMPR02025474 NanoRoute not routing straight

CCMPR02023427 SEGV in ccopt_design

CCMPR02022945 oasisOut corrupted after refinePlace

CCMPR02021837 Tool crashes while restoring the saved db

CCMPR02021529 SEGV during create_floorplan

CCMPR02021410 tQuantus SEGV during clock_design in 19.1

CCMPR02021250 Nano route crashes during diode insertion for the antenna fix

CCMPR02020915 Add fillers in postroute dbs caused tool to SEGV

CCMPR02020208 optDesign -postRoute -expandedViews crashes

CCMPR02018934 Auto track generation issue when tech lef uses FIRSTLASTPITCH

CCMPR02018117 Extra vias appear after partition

CCMPR02017530 Long secondary P/G routing to lower layer target while shorter target exist in higher metal

CCMPR02016909 verify_drc does still not detect voltage spacing violation despite recent DB fixes

CCMPR02016644 Why special route needs more overlap of a macro pin than regular route so that IQuantus finds the physical connectivity?

CCMPR02016087 **WARN: (IMPOAX-1339): Mask value for layer 'CM1' specified in technology data

CCMPR02015670 FlexH routing has too much jogging

CCMPR02015528 dbShape very slow with INSIDE, STRADDLE, and OUTSIDE

CCMPR02015460 edit_update_route_layer broken - innovus 18.12-e077_1

CCMPR02014494 SEGV during ccopt_design

CCMPR02014301 verify_drc missed VIA1.EN.10 violations when vias not centered on std cell pins pin

CCMPR02014228 defOut does not define vias used in the design, while "dumpOutVias" defines it

CCMPR02013592 Vias are missing after partition

CCMPR02013591 SEGV observed during place_opt_design with OA db

CCMPR02012767 common_ui: The edit_update_route_width command is changing/deleting the fixed via

CCMPR02011516 AddStripe could not be extended over the block unless saveDesing, freeDesign, restoreDesign are done

CCMPR02011473 CCOpt SEGV at CCOpt::Cts::Balancer::Balance, the end of globalDetailRoute

CCMPR02011408 refinePlace runtime is 22 minutes or more on 3.5M block

CCMPR02011320 View name being wrap

CCMPR02011016 Default power domain gets partition box and not boxes

CCMPR02010918 place_connected SEGVs in refinePlace with SDPs defined and unplaced

CCMPR02010514 sroute connects block pin to vertical stripes instead of horizontal stripe

CCMPR02010440 The defIn command with larger die size on rectilinear design leaves gaps in the design

CCMPR02009234 SEGV during CCOPT

CCMPR02009061 add_stripes is creating EolExt Spacing DRC violations

CCMPR02008833 SEGV during flex htree implementation

CCMPR02008610 Innovus 1812: core dump during ILM model generation

CCMPR02007904 fcroute -type power does not drop via and does not jog resulting in opens when connecting bumps to stripes

CCMPR02007435 Crash during route_design

CCMPR02007340 Innovus 1812 SEG fault when generating ILM model

CCMPR02007181 Innovus 18.11 SEGV in ccopt_design

CCMPR02004738 Crash during postroute power optimization

CCMPR02004533 To allow customized append prefix to auto generated vias (generateVias)

CCMPR02003887 Latest 181 place_opt_design SEG fault with ILM

CCMPR02003674 Incorect max VOLTAGE setup on negative bias nets

CCMPR02003218 Tool crash during interactive special route

CCMPR02003122 Innovus issues: **DIAG: invalid input to rcdb! internal node missing on net_id

CCMPR02002574 INVS 181 fails to save OA design because of missing tech layer PC (poly)

CCMPR02001610 Innovus crash during CCOpt used for buffer tree synthesis procedure

CCMPR02001589 Pipeline placement with Kmean on is not balanced

CCMPR02001117 write_lef_library outputs float instead int for ANTENNACUMDIFFAREARATIO

CCMPR02000790 Nonsensical timing on routed clk_mesh net - innovus1812

CCMPR02000738 Flip chip fcroute is not routing to all the selected bumps

CCMPR02000630 report_timing SEGVs on large flattened design

CCMPR02000571 ERROR (NREX-94) There are 10 routing layers in design, 0 layers are mapped to techfile. Please check the mapping file

CCMPR02000356 verify_drc does not flag Metal_to_Cut voltage spacing violations, internal domain's max voltage is not correct

CCMPR02000003 addStripe does not put in staple vias in particular areas

CCMPR01999693 7nm stacked vias with MAXCELLEXTENSION leaves DRCs beneath wide PG stripes

CCMPR01999622 Innovus crashes when trying to load db in an existing Innovus session

CCMPR01999385 Ports getting VSS/VDD attributes instead of tieHi/tieLo

CCMPR01999126 place_opt_design results in crash with latest Innovus 171

CCMPR01998410 preRoute extractor is generating very large cap

CCMPR01997773 synthesize_flexhible_htree run time

CCMPR01997670 IMPOPT-608 improperly reported on fully routed design preventing optDesign -postRoute from running

CCMPR01997363 delete_place_blockages continue to be accessible and not output any message

CCMPR01996818 save design crashes after using delete_clock_tree_repeaters

CCMPR01996736 verifyACLimit requires 20nm license even when 7nm license checked out

CCMPR01996074 checkPlace is crashing in 18.11-e061_1

CCMPR01995645 Wire shape is seen in GUI but part of it is not selectable/not returned by dbQuery

CCMPR01995534 Innovus crash with assembleDesign

CCMPR01995297 SEGV while loading OA db

CCMPR01995000 Floorplan step is getting crashed while sourcing addModule port file when IO port is selected

CCMPR01994489 Crash during spare cell addition on an ILM based full-chip placeOpt DB

CCMPR01994368 Unassign bump caused tool to SEGV

CCMPR01994364 INVS 18.12: Tool gives internal error IMPCCOPT-1337 during H-tree generation with customized sink list provided

CCMPR01994256 streamOut stuck when we add path metal under pin

CCMPR01993236 tQuantus with virtual metal fill fails to model increased coupling cap associated with fill

CCMPR01993072 ib_cell does not honor padding

CCMPR01992751 dbget crash in 18.11-e061

CCMPR01992241 Odd timing discrepancy between SI and non-SI

CCMPR01991422 Clock latency has no effect when we reload the DB

CCMPR01991416 assembleDesign FATAL ERROR due to port inconsistency

CCMPR01990939 setEditMode -connectPin default value is not correct

CCMPR01990712 NR should not add patch-wires on top of pins that implicitly widen the pin shapes

CCMPR01990209 routeDesign crash at RC extraction

CCMPR01990078 ccopt_design timing analysis SEGV

CCMPR01989395 DIAG errors from add_tieoffs emitted by CCOpt code even though running place_opt_design

CCMPR01989345 read_physical -add_lefs generates ERROR: (IMPSE-110)

CCMPR01989030 create_route_blockage in 18.12 rounds off coordinates

CCMPR01988547 Need an official way to open the Timing Debug window from a command

CCMPR01988343 editPowerVia to create maximum number of cuts in the intersection (w/o changing wire shape)

CCMPR01988254 Innovus is getting crash while ccopt_design

CCMPR01987794 CCOpt segmentation fault

CCMPR01987611 synthesize_ccopt_flexible_htrees: long runtime at "Computing placement data for flexible H-tree"

CCMPR01987471 Post-route optimization hangs with the ERROR: (IMPSYUTIL-2)

CCMPR01987116 18.1x stops on setViaEdit -allow_geom_drc 1 > /dev/null

CCMPR01985524 Quick abstract inference does not create metal blockages in 18.1

CCMPR01983228 write_lef_abstract does not color pin shapes on M1 correctly

CCMPR01982662 Question on messages printed when invoking the timeDesign command

CCMPR01982246 streamOut -merge is creating a GDS with multiple top structures breaking downstream flows

CCMPR01982216 Spelling error in the "gui_dim_foreground -lightness_level medium" option

CCMPR01982090 .globals file cannot be read back without error through Innovus

CCMPR01981568 181/182 DIAG and SEGV during create_clock_tree_spec

CCMPR01981106 Errors during eco_design with 17.15

CCMPR01980067 Wire widening creates minStep violations

CCMPR01979552 Innovus tool changes orientation when moving pad cells

CCMPR01979198 Innovus 18 crashes on setNanoRouteMode -routeUseAutoVia true

CCMPR01977245 remove_assign/init_remove_assign is not able to remove assign statement

CCMPR01976209 synthesize_ccopt_flexible_htrees crashed with 18.11,18.12 and 18.20

CCMPR01974522 write_lef_library creates invalid LEF file on cells with MUSTJOIN pins.

CCMPR01974303 place_opt_design hangs during in2reg path group optimization

CCMPR01974294 zoom to metal fill causes SEGV

CCMPR01973819 write_lef_library creates a corrupted lef file

CCMPR01973725 addInst snap to one row below the expected row

CCMPR01972187 Innovus 18.1 extraction with tQuantus is failing

CCMPR01971806 Response time of Timing Debugger is very slow

CCMPR01971303 Min cut in LEF for Innovus 18.1 causing DRC

CCMPR01970959 NanoRoute to connect preroutes without using trim (on track next to wide metal)

CCMPR01970864 Status attributes regarding status of the current design

CCMPR01970765 DRV preCTS optimization using normal buffers for cross domain paths

CCMPR01970010 How can we write out a netlist, by excluding PG pins of instances from BE ECO db?

CCMPR01969915 Innovus IO PAD routing using FCROUTE leaves many opens and thousands of DRCs

CCMPR01969845 editPowerVia does not always pick the correct solution

CCMPR01969784 Wrong IEEE1801 PST handling in Innovus while merging multiple power states.

CCMPR01969777 CCOpt places clock buffer w/via pillar beneath wide power rail creating downstream DRCs

CCMPR01969257 synthesize_ccopt_flexible_htrees hangs

CCMPR01968936 Tool crashing while updating timing

CCMPR01968395 addStripe crashed in 18.11-e061_1

CCMPR01968362 oasisOut outputting duplicate text labels on bump shape resulting in DRC errors about off center text

CCMPR01967420 sroute is creating shorts with std cell geometries

CCMPR01967106 NR is not able to clean up Macro pin access DRCs

CCMPR01966885 Innovus 18.1 hangs during via pillar insertion

CCMPR01966833 Routing QOR degradation 18.11 vs 17.14

CCMPR01965947 **ERROR: (IMPSYC-194) message flagged for the addHaloToBlock command needs improvement

CCMPR01965602 Via pillar y-pitch not honored

CCMPR01964727 addStripe hangs with use_fgc true

CCMPR01964425 write_db stops with ERROR: (UI-476) message

CCMPR01964258 Postroute optimization hangs due to the addFiller command

CCMPR01963241 NR/ecoRoute fails to resolve M1 trim metal violation

CCMPR01963228 18.1 verify_drc flags M5/M7 directional spanlength spacing violations that PVS does not

CCMPR01963072 Cannot reset modify_ndr -minCut to value 1

CCMPR01962601 routeDesign exceeds 800GB memory usage: memory jump in TDGR

CCMPR01962435 DB access command keeps incorrect placement halo

CCMPR01962315 Innovus crashing at init_design

CCMPR01961813 Documentation for trace_through_to is inadequate

CCMPR01961026 Mesh-based secondary PG routing leaves lots of DRCs

CCMPR01960572 place_opt_design is modifying rectilinear floorplan boundary

CCMPR01960045 Timing in 18.1 more optimistic than 17.15

CCMPR01960041 Placement resulting in V0 violations with colored V0

CCMPR01959418 editPowerVia runtime increased 84 times from 17.1 to 18.1

CCMPR01959360 INNOVUS crash while saving OA design

CCMPR01959050 Highlight PD gives SEGV

CCMPR01958208 Deletion of unwanted pgTerm caused all bumps unassigned

CCMPR01958079 passiveFill shapes add multiple shapes overtop each other with successive runs

CCMPR01956970 Crash with extractRC called from Innovus

CCMPR01954979 Innovus: init_design failing with IMPOAX-929 for hierarchical PCell in the express PCell cache

CCMPR01954599 optDeisgn -postroute segv

CCMPR01954371 How to add/query object1/object2 information using create_marker/get_db?

CCMPR01954079 place_opt_design -opt takes 90hrs for multiBitFlopOpt and freeFlopMerge flow

CCMPR01953839 Abort during route_design in 18.11-e055_1

CCMPR01953753 NanoRoute adds unnecessary patch wire

CCMPR01953010 routeDesign fails during parasitic extraction

CCMPR01952429 Innovus IO PAD routing using fcroute does not complete

CCMPR01952368 Placement is creating overlap of cell V3 OBS SPACING 0 with V3 PG

CCMPR01951940 optDesign -postRoute results in hang/DRC explosion

CCMPR01951176 refinePlace should not crash when design is not in memory

CCMPR01951135 Crash in saveDesign

CCMPR01950404 Instant crash with report_obj_connectivity -ports

CCMPR01949858 addRepeaterByRule -postRoute will not add buffer on net that goes around macro and -preRoute adds right at the sink only

CCMPR01948429 Part 2: 17.15 routing violations from via-down to memory pins

CCMPR01948238 Crash with the violationBrowserHide command

CCMPR01948236 verify_drc is wrong for ARRAYSPACING … WITHIN … ARRAYWIDTH

CCMPR01947984 verify_drc misses cut EOL violation with 18.11 version but catches in 17.1x

CCMPR01947870 Pin access took long time for two cells with setNanoRouteMode -routeExpWithTrimMetal

CCMPR01947572 add_stripes do not error out when syntax is wrong

CCMPR01945584 TCL execution continues **ERROR: (IMPLIC-90) to terminate TCL script execution

CCMPR01944678 M2/M3 power staples added with the addStripe command are extending outside of the core boundary of the design

CCMPR01944534 verify_drc very slow taking multiple days

CCMPR01944340 ECO routing to fix ARRAYSPACING violations marked by verify_drc

CCMPR01944168 Buffer budget violations seen when using new mixed buffer/inverter flow in extreme flow

CCMPR01944100 streamOut crash

CCMPR01943523 Stack trace during timeDesign -reportOnly

CCMPR01943135 Tool crashes when propagate_activity is run

CCMPR01941965 171/181: SEGV during postroute optimization during ECO shielding

CCMPR01940993 place_opt_design crash of large chip

CCMPR01940925 tQuantus skips special nets which caused tQuantus and QRC correlation issue

CCMPR01940096 Cell Viewer does not appear to display cells of CLASS COVER

CCMPR01939977 Floorplan core bbox modified during design import without warning

CCMPR01939612 check_pin_assignment does not output report to screen

CCMPR01938807 skewClock -postRoute crashes

CCMPR01937840 SEGV ERROR while cloning

CCMPR01937708 optDesign -drv prefers AOBs over secondary islands for buffering

CCMPR01937352 editPowerVia drops a via having Cut Spacing violation with STD cell geometry

CCMPR01937069 optDesign not buffering HFN nets in secondary domain (MSV aware topology)

CCMPR01936562 Detail routing jogs on NDR nets creating DSLSpc violations

CCMPR01934572 18.1 create_route_blockage -rects runs much slower than create_route_blockage -area in 17.1x

CCMPR01934422 False My.S.2.1.1 rules flagged by verify_drc

CCMPR01934242 Detail Routing crashes in 17.15-e018

CCMPR01934173 NanoRoute falls over in 18.1 with ERROR (NRAG-28) Cannot do strict search

CCMPR01933623 High memory usage and runtime during editPowerVia

CCMPR01933608 addFiller creates real and false checkPlace violations

CCMPR01933601 CCOpt crashed during clustering

CCMPR01933584 ccopt_design -cts crash at clustering

CCMPR01933156 editAddVia adding special Via on a regular net

CCMPR01933006 add_io_buffers command does not add buffers for output ports driven by power or ground net

CCMPR01931842 checkPinAssignment fails to catch some violations

CCMPR01931763 routeDesign crashing during optimization when run with setNanoRouteMode -routeWithOpt true

CCMPR01931496 Innovus hanging on saveDesign

CCMPR01930541 Ostrich core dump when reading sign off spef file

CCMPR01930205 Innovus creates unspecified "vdd" power net

CCMPR01929024 routeDesign to fix more cut Spacing violations

CCMPR01928244 Big slow down using setViaGenMode -ignore_DRC false, with editPowerVia

CCMPR01926752 Ostrich hangs when reading signoff spef file for several blocks

CCMPR01926556 VIA3.R.4:M4 Calibre Drc not reported by Innovus

CCMPR01926442 Tracks not re-created when using filter option with oaIn

CCMPR01925327 Almost 30K M1 DSLCOL violations with newer builds where 17.14-e040_1 routed near clean

CCMPR01925158 Hierarchical upf - top level scope contains redundant set_port_attribute from sons

CCMPR01924649 ERRORs due to set_max_delay -from clock -to clock in constraints: units and missing analysis views

CCMPR01924632 Nanoroute shield wire DRC violations

CCMPR01924207 place_opt_design is using high Memory after global placement

CCMPR01923810 verify_drc fails to catch VIAINPINONLY DRC violation

CCMPR01923713 Support layer based spacing constraint in pin assignment

CCMPR01923446 18.10–non-determinism in POD

CCMPR01923159 editPowerVia exits possibly due to memory issue

CCMPR01922769 Current being incorrectly distributed between the primary ground pin and the bulk ground pin

CCMPR01921606 SDP stack splits when it comes across prefixed cells

CCMPR01921587 tQuantus extraction of clock via pillars results in miscorrelation of cap/res vs tQRC/iQRC/QRC

CCMPR01921566 Innovus is not able to resolve cutSameMaskSpacing violations

CCMPR01921051 route_fix_signoff_drc to warn and list global routed or unconnected nets

CCMPR01920786 **ERROR: (IMPCCOPT-1222):While running synthesize_ccopt_flexible_htrees in 18.1

CCMPR01920382 check_place should not report fixed instances inside soft placement blockage as violations

CCMPR01920080 Stack Trace Error in Stylus flow

CCMPR01919706 addEndCap long runtime in large design

CCMPR01919531 Innovus crashes on loadFPlan command

CCMPR01919383 False trim to trim violation in verify_drc

CCMPR01919238 Manual editing is not honoring the track color for wire color assignment

CCMPR01919045 Unacceptable long run time for read liberty

CCMPR01918930 check_drc did not flag M4.R.7

CCMPR01918883 18.10-a087_1-non-determinism in CCOpt spine flow

CCMPR01918786 timeDesign -preCts segv

CCMPR01918379 Shielding Percentage on clock nets drops significantly from 94% after CTS to 60% at postroute

CCMPR01918011 False short between SADP_FILLS and unused pin in verify_drc

CCMPR01917899 Incremental UPF having duplicate information

CCMPR01917611 optDesign does not honor preserveModuleFunction

CCMPR01917303 17.15 routing violations from via-down to memory pins

CCMPR01916693 Congestion Repair not occurring on 4 metal layer design

CCMPR01916619 optDesign -postRoute SEGV

CCMPR01916593 Die size change with saveDesign and restoreDesign Back with set fpgOddEvenSitesRowConstraint 2

CCMPR01915378 assign_partition_pin inefficiently assigning pins

CCMPR01915338 Tool is throwing **DIAG message while running "routeDesign -trackOpt"

CCMPR01914741 placeDesign -noPrePlaceOpt takes 7 hours on design with 7 insts

CCMPR01914726 Crash in route stage due to net integrity problem from global routing

CCMPR01914599 171/181 tool add AO cell which are not needed, such cell impact negatively frequency target

CCMPR01914222 preCTS useful skew is leaving many skewing opportunities

CCMPR01914032 Cell Viewer incorrectly displays asymmetric vias

CCMPR01913386 Some SDP stacks are not being pin-aligned

CCMPR01913232 scanReorder with inter-chain swapping turned on made no changes to the domains where it was enabled

CCMPR01912800 preroute_opt clock tree expansion adds repeaters in the incorrect power domain

CCMPR01912273 Buffer add by opt resulting in CLP violations

CCMPR01912257 Innovus not reporting Mx.En.10.1 enclosure violation on M7

CCMPR01911530 Patch wires getting added create DRC violations. Patch wires not needed

CCMPR01911496 Tempus to return prompt after read_db

CCMPR01911308 ccopt_design -cts crash after clustering

CCMPR01911022 ILM internal paths showing up at the parent level by report_timing

CCMPR01910144 17.14 place_opt_design SEGV during extraction

CCMPR01909561 INNOVUS: Make common report_area_summary command across tools

CCMPR01908841 Violation browser GUI should not change focus when hide/show/show only this type is selected

CCMPR01908649 verifyPowerDomain reports a false IMPMSMV-8301 for isolation location fanout

CCMPR01908273 G2 power routing is not connecting properly to pins

CCMPR01906436 Loading db after setting set_db oa_update_mode auto results in pins having placement status of cover instead of fixed

CCMPR01906356 optDesign leaving many nets unbuffered in VDD_MX domains (MSV gas-station topology)

CCMPR01906318 sroute runtime 7X slower than 17.12 in 17.13 or newer

CCMPR01906232 Spelling and grammatical mistake in IMPSE-124 message

CCMPR01905471 *DIAG:(Missing Adj): + 0.066 & ERROR: (TA-1029): a reporting error… during report_timing

CCMPR01904798 Innovus is crashing during source group allocation in CTS

CCMPR01904562 Innovus does not save the library path in relative path format using the saveDesign -relativePath command

CCMPR01904499 Moorea isInstColorConflictLegal() should not flip instance color if no DRC

CCMPR01902667 v2 cut spacing violations after place_opt_design

CCMPR01902264 Innovus Crash during timeDesign with Multi-CPU option with Innovus-17.1

CCMPR01902203 Tool crashes while running check_connectivity

CCMPR01901702 place_opt_design crash with m_heapCount && m_nodeList messages

CCMPR01901485 Select-all followed by copy in Innovus GUI object attributes field only fills copy/paste buffer not middle-mouse

CCMPR01901252 Stylus to please enable running of flow without reporting followed later with reporting

CCMPR01900393 NR creates layer jumps that cannot fix process antenna violation

CCMPR01900055 reportPowerDomain gives inconsistent voltage values

CCMPR01900044 Innovus does not mark M4.S.27 violations by check_drc

CCMPR01899252 lremove functionality inconsistent between Tempus/Voltus/Genus/Innovus legacyUI vs CUI

CCMPR01899219 Levelshifters not getting inserted and few of the nets in this design not getting clamped as per default cpf rule

CCMPR01898681 get_db multiline -if clauses output extra newlines to stdout

CCMPR01898530 Innovus crash during PlaceOpt with Block ILM

CCMPR01897629 ERROR IMPLF-381 message needs to be flagged for standard cells with "CLASS CORE" property only

CCMPR01897349 optDesign -postRoute: Timing degradation seen within ecoRoute call

CCMPR01896657 sVIA and sWIRE are modified outside the yellow box in parallel edit

CCMPR01895113 Innovus creates max via stack DRCs which are not reported by Innovus as violations

CCMPR01894559 Innovus crashes if the number of objects reported is more than 536870909

CCMPR01894510 17.1x ecoRoute adding unnecessary M3 patch metal

CCMPR01894033 Better suggestion for attachTerm and attachModulePort

CCMPR01893695 Tool is not honoring the list in -exclude_elements for the level_shifter rule correctly

CCMPR01893633 Crash in setIntegRouteConstraint

CCMPR01890864 Mincut DRC error not seen by Innovus as violation

CCMPR01890572 dont_touch of hinst cannot be removed

CCMPR01890331 Malformed Via from VIAGEN

CCMPR01889179 attachTerm run time exponential degradation

CCMPR01887920 Ccopt_design -cts hangs after clustering

CCMPR01887249 runtime issue for starting level-shifter placement with spgOption.shifterMode

CCMPR01886644 Need Common UI support for these options for setOptMode

CCMPR01882839 Multipass CTS configured with opt_ignore property crashes

CCMPR01882585 sroute creates DRC

CCMPR01881856 TNS x3 worse for reselection all compared to slack based reselection (-310ns vs -101ns)

CCMPR01880659 Support UPF set_port_attribute feedthrough and unconnected

CCMPR01880138 Crash with multiple resize_floorplan commands (GUI)

CCMPR01879487 Long saveDesign runtime on design with 1.5 M instances

CCMPR01879298 How to increase precision in verify reporting

CCMPR01876164 Innovus routes to power pin inside routing blockage (and creates shorts)

CCMPR01873951 Enhance wire editor to accept a list of vias to ignore

CCMPR01873950 SEGV in report_timing after assembleDesign

CCMPR01869930 verify_drc gets CUTCLASS wrong for ARRAYSPACING

CCMPR01869627 Innovus hangs during place_opt_design

CCMPR01869304 SEGV crash at optDesign -postCTS -hold in 17.12 version

CCMPR01868480 verifyPowerVia report incorrect distance in report file, correct one in Violation browser

CCMPR01867643 saveDesign takes roughly an hour

CCMPR01867132 Crash during restoreDesign of an assembled design

CCMPR01865552 171/181 verifyConnectivity does not report unrouted net when IO pin are unplaced

CCMPR01855635 PWR nets are not pushed down into partition as expected

CCMPR01854089 Enhancement of Via pillars to support power routing

CCMPR01852129 Innovus needs controls for not added EEQ cells in the netlist (LVS requirement)

CCMPR01851275 17.12 commit_power_intent leaving 15k retnFlop vdd_ext open but 15.24 build is not

CCMPR01849939 DRC increase at post-route opt due to high local density

CCMPR01847215 write_timing_model SEGVs in 17.11 and early versions of 17.12/18.1

CCMPR01842874 Innovus route_design QOR degrades from 16.21 to 17.1 version.

CCMPR01840991 addFiller needs to be multithreaded

CCMPR01839568 place_opt_design crash

CCMPR01839093 "ccopt" leaves too many max_tran violation

CCMPR01834721 ecoRoute -fix_drc area to route open nets in area w/o any area limitation

CCMPR01833756 Floorplan code to provide callback registration for floorplan changes (like placement-blockages, tracks)

CCMPR01833617 verify_drc reports false LB min witdh error

CCMPR01829781 Post CTS hold fixing does not fix all violation when min_delay is on module pin

CCMPR01817952 read_stream should also support oasis format

CCMPR01811286 Get huge numbers of TCLCMD-513 warnings when using get_db to query the .clocks attribute of a pin

CCMPR01810483 create_ccopt_clock_tree_spec hangs

CCMPR01807374 verify_drc miss DRCs to diagonal special route

CCMPR01807373 Encounter saveNetlist io port ordering issue

CCMPR01802847 Innovus crashes during delay calculation in addMetalFill

CCMPR01794219 streamOut oasisOut mapfile enhancement needed for mapping SADP and trimmetal fill shapes

CCMPR01792686 Custom shape polygon is not being saved in Common UI and even object attribute is not working on it

CCMPR01790128 Adding via pillar run time issue

CCMPR01789477 write_db/saveDesign does not adequately sanitize comments in constraint files

CCMPR01787945 The summaryReport command is reporting box area for pad cell instead of reporting rectilinear area

CCMPR01776838 get_db pg_nets reports tie nets under pg

CCMPR01772729 Adding -rc_corners option for write_extraction_spec command

CCMPR01758143 editAddTrimMetal should allow pin as argument with layer control rather than selected object

CCMPR01749914 Error TECHLIB-9067 while reading in RAM .lib-File

CCMPR01747858 fixHold estimates not matching with final summary due to old CTE SOCV variable

CCMPR01740416 fcroute serial_pad_routing with star connectivity

CCMPR01740161 Request for a tcl command that will select and attach any object to the cursor

CCMPR01714367 Request way to remove custom layers from the Custom Layer tab of Color Preferences Gui

CCMPR01708063 createPinGroup -spreadPin option does not work as documented

CCMPR01699424 oasisOut: How to record the instance information directly on an attribute 'instName' rather integer attribute 300

CCMPR01682932 time_design not honoring opt_time_design_expanded_view=true

CCMPR01667971 saveDesign takes very long time when setSIMode -skip_tw is in use

CCMPR01665686 The path_group target slack multiplies by a factor of 1000 with each write_db / read_db cycle

CCMPR01613077 OAX gets the layer order wrong from standard via

CCMPR01602674 Issue with drouteStrictlyHonorObsInStandardCell true

CCMPR01567410 Attributes table for numerous selected objects

CCMPR01561575 oasisOut is shifting BUMP locations

CCMPR01554953 isLogCommand not documented or in the help

CCMPR01540198 Enhancement: add command to show a path and name to the currently loaded DB

CCMPR01516053 expandedViews does not work with timeDesign -signoff

CCMPR01465935 createLib should also create cdsinfo.tag file.

CCMPR01370636 Preference settings in Instance Based schematic and Clock Tree Debugger windows

CCMPR01290790 redirect -variable takes long time to complete in Tempus

CCMPR02122181 Unable to run floorplanning

CCMPR02120749 User set timing derates are getting overwritten

CCMPR02119829 scandef errors while restoring flattened ILM DB

CCMPR02118446 Innovus 19.10 is locking up during ccopt_design CUI

CCMPR02118241 selectInst crashes in 19.11_e088

CCMPR02116891 Fatal crash during place_opt_design with Innovus 19.11-e081_1

CCMPR02115286 place_opt crashing during scheduling file restore in ECF

CCMPR02114856 Coloring is crashing at NR::sort_inst() on one of the designs

CCMPR02114633 The add_fillers command causes Innovus 19.1 to hang for customer in tapeout. Works with 18.13-s088_1.

CCMPR02113715 select_bump -net <netname> is not selecting the corresponding bumps

CCMPR02112033 SEGV on a design

CCMPR02111670 detachTerm SEGV due to user usage error

CCMPR02111184 place_opt_design -opt crashes after SKP initialization

CCMPR02110538 assignPtnPin SEGV

CCMPR02110373 optDesign got crashed at spsInstMapLLG::getContextDemandInRange

CCMPR02110294 Nanoroute creates patch wires on _SADP_FILLS_RESERVED in N5 node

CCMPR02109985 Innovus crashed in optimization during DrvOpt

CCMPR02109757 SEGV during "routeDesign -trackOpt"

CCMPR02108858 Run eGR for better congestion prediction

CCMPR02108852 Timing still jumps a lot if redo full eGR-steiner with incr-eGR-steiner on

CCMPR02108281 Innovus does not connect supply pins from apply_power_model -supply_map

CCMPR02107699 Crash at the AddStripe command

CCMPR02107624 1911 place_opt_design crash

CCMPR02107247 Early global router bad clock routing with NDR tracks defined

CCMPR02106808 fterm location changed after write_db and then read_db

CCMPR02106711 SEGV during iSpatial

CCMPR02106530 Tool crash at dbsStripBoxGroupMgr::iterator globalDetailRoute due to missing power connection in netlist

CCMPR02105917 18.13 CCOpt SEGV on "RefinePlaceCaller::ReportMovementHelper(const InstRec& instRec,"

CCMPR02105502 saveDesign crashing with 19.1-p002_1

CCMPR02105497 addEndCap crashing randomly in mixed placer flow with 19.11

CCMPR02105432 **WARN: (IMPSC-1026): Instance pin %s connects to net %s with multiple (5) drivers

CCMPR02104875 place_opt_design crash

CCMPR02104801 19.11 postcts crash before hold fixing

CCMPR02104799 19.11 report_power crash

CCMPR02104685 Innovus crash in place_opt_design 18.13 CUI

CCMPR02104677 Innovus crash with placeInstance of large delay cell

CCMPR02104565 Innovus crashing right after checkFPlan with 19.11

CCMPR02104540 Crash during routeDesign

CCMPR02104528 Bus Planning - place_opt_design adds buffers outside busGuide

CCMPR02104489 Design load crashing in 18.15

CCMPR02103946 eco_oa_design gives error in 18.14

CCMPR02103187 UPF file duplication lines on set_iso*

CCMPR02102533 Need Secondary PG connection to extend top stripe to switch cell pin

CCMPR02102523 Tool crashes during the optDesign -postCTS command

CCMPR02102514 verify_drc reports a false EOL-Keepout violation

CCMPR02102399 earlyGlobalRoute crashed due to user's incorrect -earlyGlobalMinRouteLayer setting

CCMPR02102357 Innovus is unable to generate DRC clean multicut power vias

CCMPR02102330 Power routing is not adding vias in 18.14-e070 and later

CCMPR02101742 signoffTimeDesign command is checking out two Tempus licenses when only one is required

CCMPR02101735 Tempus eco crash during drv optimziation

CCMPR02101728 Filler node crashing while executing the verifyLitho command

CCMPR02101712 Crash during global placement

CCMPR02101422 Need help on Tempus TSO tool crash during invocation of eco_opt_design -hold

CCMPR02101155 savePartition crash in 19.71-e003

CCMPR02101131 Crash during routeDesign -highFrequency

CCMPR02101005 Innovus crash with globalDetailRoute during the Route stage

CCMPR02100922 SEGV when "place_opt_design -no_pre_place_opt" from iSpatial DB

CCMPR02099805 M4 EOL keepout violations

CCMPR02099791 M2 EOL keepout violations

CCMPR02099754 Place stage in ccopt_design command crash

CCMPR02099753 routeDesign reports ERROR: NR History Map is not available in dbs

CCMPR02099708 optDesign postRoute timing difference between fullDC timing and optimization

CCMPR02099683 **ERROR: (IMPTCM-4) happens in create_proto_model

CCMPR02099655 Extraction crashes when running report_timing in 19.71-e003_1

CCMPR02099500 place_opt_design hangs after issuing **WARN: (IMPSP-9089): Feature 'LEF ROWPATTERN' is obsolete

CCMPR02099187 Utilization test - EGR correlation

CCMPR02099049 TQuantus crash inside routeDesign

CCMPR02099034 Editpowervia creates M2 Same metal aligned cut violations with cell geometries

CCMPR02098961 FC route leaving a mess for some bumps when solution seems simple